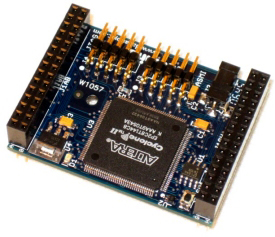

Niomite Cyclone II™ EP2C8 Controller/FPGA Module

Niomite User Guide

Niomite User Guide

(1.6 MB)

Niomite Design Readme

Niomite Design Readme

(464 KB)

Niomite 2C8 Nios II Design QII 6.0 SP1

Niomite 2C8 Nios II Design QII 6.0 SP1

(9.1 MB)

Niomite 2C5 Nios II Design QII 6.0 SP1

Niomite 2C5 Nios II Design QII 6.0 SP1

(9.1 MB) – stand-alone version, no Nios II

Niomite Schematic revb

Niomite Schematic revb

(1.4 MB)

Information :

The Niomite module allows implementation of FPGA logic functions and/or Altera® Nios II processor operation in the smallest possible form factor. Niomite provides the following circuits to support a small footprint FPGA based controller:

- 512K X 8 SRAM

- EP1S4 FPGA serial loader (FPGA and Nios II boot)

Niomite modules also supports the ![]() specification (master or slave half card, 60 pin), and can interface with other modules designed to that specification. The Niomite kit includes an FPGA programmer and power supply, and provides all the hardware items which are necessary to start designing with and evaluating the powerful features of Altera® Cyclone II FPGA devices.

specification (master or slave half card, 60 pin), and can interface with other modules designed to that specification. The Niomite kit includes an FPGA programmer and power supply, and provides all the hardware items which are necessary to start designing with and evaluating the powerful features of Altera® Cyclone II FPGA devices.

Module Details :

- Altera EP2C8 Cyclone II FPGA, in –C8 speed grade and 144 pin TQFP package.

- Separate programming ports (ASMI flash interface and JTAG interface).

- Reset and voltage monitor IC which provides 400mS reset pulse.

- Reset push-button switch.

- 44 input/output and 7 input pins available.

- 1 discrete indicator LED (green).

- Clock oscillator (25 MHz).

compatible design.

compatible design.- EPCS4 (4Mbit) serial flash for FPGA configuration (and Nios II software).

- 512K x 8 bit (4Mbit) SRAM for Nios II program execution and dynamic data storage.

Quartus II Starter Design :

- Created using Quartus II ver. 6.0 SP1.

- Nios II processor defined.

- All module pins are defined in top level schematic project file.

- Memory test with results indicated to LED.

- FPGA load from EPCS4.

Kit Package Contents :

- Niomite Cyclone II EP2C8 module..

- Wall mount 3.3VDC/2A switching supply.

- Altera USB Blaster FPGA programmer.

Images :

Product Data :

| FPGA | EP2C8 |

| Logic Elements (apprx. 50 gates per LE) | 8256 |

| M4K RAM Blocks (4 Kbits + parity) | 36 |

| Total RAM Bits | 165888 |

| PLLs | 2 |

EP3C25 module

| CMC2001-2M-8 | EP2C8 module | 139.00 US |

| CMC2001-2M-8-KU | EP2C8 USB Blaster kit | 369.00  |

Dallas Logic

Dallas Logic