EP3C25 FPGA/CONTROLLER MODULE

# **CMCS002 User Guide**

2300 McDermott #200-305 Plano, TX 75025 <u>www.dallaslogic.com</u>

Release 2.0- October 2009 ©2009 by Dallas Logic Corporation. All rights reserved. This document is the property of, and is maintained by Dallas Logic Corporation. Please email any questions, corrections, or suggestions to <u>requests@dallaslogic.com</u>, or see our forum located online at <u>www.dallaslogic.com</u>. Dallas Logic Corporation shall under no circumstances be liable for damages or related expenses resulting from the use of this document. Your use of this information indicates your understanding of, and agreement with the disclaimer located on the last page of this document.

| Revision | Author | Date       | Description                                            |

|----------|--------|------------|--------------------------------------------------------|

| 0.1      | ET     | 06-24-2009 | Initial draft for review.                              |

| 0.2      | JT     | 07-08-2009 | Updated starter design sections                        |

| 1.0      | ET     | 07-08-2009 | First release of User Guide                            |

| 2.0      | ET     | 10-14-2009 | Added pin information diagram (limitations on IO pins) |

|          |        |            |                                                        |

|          |        |            |                                                        |

|          |        |            |                                                        |

|          |        |            |                                                        |

|          |        |            |                                                        |

|          |        |            |                                                        |

### Table of Revisions

# **Table of Contents**

| <ul> <li>1.1 CMCS002 Quick Start</li> <li>2 Component Descriptions</li> <li>2.1 Altera Cyclone III Device Resources.</li> <li>2.2 CMCS002 Devices.</li> <li>2.2.1 EPCS16 serial flash.</li> <li>2.2.2 512K X 8 SRAM.</li> <li>2.2.3 USB Interface.</li> <li>2.2.4 JTAG and ASMI Programming Headers.</li> </ul> | 7<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.1       Altera Cyclone III Device Resources.         2.2       CMCS002 Devices.         2.2.1       EPCS16 serial flash         2.2.2       512K X 8 SRAM.         2.2.3       USB Interface.                                                                                                                 | 8<br>9<br>9<br>9<br>9<br>9<br>                |

| 2.2         CMCS002 Devices           2.2.1         EPCS16 serial flash           2.2.2         512K X 8 SRAM           2.2.3         USB Interface                                                                                                                                                             | 9<br>9<br>9<br>9<br>9<br>10<br>10             |

| 2.2.1       EPCS16 serial flash         2.2.2       512K X 8 SRAM         2.2.3       USB Interface                                                                                                                                                                                                             | 9<br>9<br>9<br>9<br>10<br>10                  |

| 2.2.2 512K X 8 SRAM                                                                                                                                                                                                                                                                                             | 9<br>9<br>9<br>10<br>10                       |

| 2.2.3 USB Interface                                                                                                                                                                                                                                                                                             | 9<br>9<br>10<br>10                            |

|                                                                                                                                                                                                                                                                                                                 | 9<br>10<br>10                                 |

| 2.2.4 JTAG and ASMI Programming Headers                                                                                                                                                                                                                                                                         | 10<br>10                                      |

|                                                                                                                                                                                                                                                                                                                 | 10                                            |

| 2.2.5 Reset Circuit                                                                                                                                                                                                                                                                                             |                                               |

| 2.2.6 FPGA User IO Bank Voltage                                                                                                                                                                                                                                                                                 | 10                                            |

| 2.2.7 Indicator LED                                                                                                                                                                                                                                                                                             | -                                             |

| 2.2.8 CMCS002M IO Pin Information                                                                                                                                                                                                                                                                               | 11                                            |

| 3 Setup and Programming                                                                                                                                                                                                                                                                                         | 12                                            |

| 3.1 CMCS002 Module Setup                                                                                                                                                                                                                                                                                        | 12                                            |

| 3.1.1 Altera Software and FPGA Programmer                                                                                                                                                                                                                                                                       | 12                                            |

| 3.1.2 CMCS002 FPGA Programming Instructions                                                                                                                                                                                                                                                                     | 13                                            |

| 3.1.3 Cyclone III Pin Voltage Sensitivity (over-shoot and under-shoot)                                                                                                                                                                                                                                          | 13                                            |

| 3.1.4 5V Interfacing With Cyclone III                                                                                                                                                                                                                                                                           | 13                                            |

| 3.1.5 CMCS002 Module Power                                                                                                                                                                                                                                                                                      | 14                                            |

| 3.1.6 Cardstac Support – CMCS002 Design                                                                                                                                                                                                                                                                         | 14                                            |

| 3.1.7 Altera Reference Documents                                                                                                                                                                                                                                                                                | 15                                            |

| 4 CMCS002 Design Information                                                                                                                                                                                                                                                                                    | 15                                            |

| 4.1 Pin Function Mapping                                                                                                                                                                                                                                                                                        | 15                                            |

| 4.2 Quartus II Starter Design                                                                                                                                                                                                                                                                                   | 18                                            |

| 4.2.1 CMCS002 Starter Design File Install                                                                                                                                                                                                                                                                       | 20                                            |

| 4.2.2 Quartus II Tutorial Instructions                                                                                                                                                                                                                                                                          | 20                                            |

| 4.2.3 CMCS002 Design Schematic                                                                                                                                                                                                                                                                                  | 20                                            |

| 5 Mechanical Dimensions                                                                                                                                                                                                                                                                                         | 21                                            |

| 6 Ordering and Technical Help                                                                                                                                                                                                                                                                                   | 22                                            |

| 6.1.1 CMCS002 Ordering Information                                                                                                                                                                                                                                                                              |                                               |

| 6.1.2 CMCS002 Module Technical Help                                                                                                                                                                                                                                                                             |                                               |

| 6.1 | .3 Wa  | arranty Information |

|-----|--------|---------------------|

| 7   | Discla | aimer23             |

# **List of Figures**

| Figure 1-1 CMCS002 Module                        | 6   |

|--------------------------------------------------|-----|

| Figure 2-2-1 CMCS002 Silkscreen Legend           |     |

| Figure 2-2-2 PCB Pin Orientation                 | 8   |

| Figure 2-2-3 CMCS002M Pin Functions              | .11 |

| Figure 4-4-1 Recommended Functional Pin Grouping | .17 |

| Figure 4-4-2 Starter Design Block View           | .18 |

| Figure 4-4-3 Nios II block symbol                | .19 |

| Figure 5-5-1 CMCS002 Mechanical Dimensions       | .21 |

# **List of Tables**

| Table 2-1 EP3C25 FPGA Resources                        | 8  |

|--------------------------------------------------------|----|

| Table 2-2 Nios II Performance and Resource Utilization | 9  |

| Table 3-1 CMCS002 Power Input Fusing                   | 14 |

| Table 4-1 Recommended Pin Mapping (16 bit interface)   |    |

| Table 6-1 CMCS002 Part Numbers                         |    |

|                                                        |    |

# 1 Introduction

The purpose of this document is to provide users of the CMCS002 module a guide for performing power up, programming, and general circuit and connector identification. The CMCS002 is primarily intended as an FPGA module (Altera EP3C25), but also provides support circuits to enable operation as an Altera Nios II controller. The following list identifies the primary feature set of the CMCS002 module:

- Altera® EP3C25 FPGA, in -C8 speed grade and 256 pin BGA package.

- Separate programming ports (ASMI flash interface and JTAG interface).

- Reset and voltage monitor IC which provides 400mS reset pulse.

- Reset push-button switch.

- 109 input/output pins available on stack-through header.

- 3 discrete indicator LED (red, yellow, green).

- Clock oscillator (25 MHz).

- . **cardstac** compatible design. Populated with stack-through connector.

- EPCS16 (16Mbit) serial flash for FPGA configuration and Nios II software.

- 512K x 8 bit (4Mbit) SRAM for Nios II program execution and dynamic data storage.

- USB 2.0 full speed port (FT232RL).

The CMCS002 FPGA kit has everything you need to start designing with and evaluating the powerful features of Altera® Cyclone III<sub>TM</sub> FPGA devices. The kit provides an Altera Byte Blaster II or USB Blaster FPGA programmer and a 3.3V power supply. Individual CMCS002 modules (no kit components) are also available. Whether you want to learn about FPGA design, or have a specific design implementation to complete, this FPGA module will jump-start the your own Cyclone III<sub>TM</sub> design efforts. Your CMCS002 kit includes the following items:

- CMCS002 module

- Wall mount type 3.3VDC/2A switching power supply (US or Asian/European model, depending on geographic location)

- Altera® ByteBlaster II or USB Blaster FPGA programmer

Figure 1-1 CMCS002 Module

### 1.1 CMCS002 Quick Start

To quickly see your CMCS002 module function, complete the following steps:

- 1. Locate your CMCS002 module so as to not short any of the pins on the bottom of the PCB. Make sure to clean away any loose wire or solder from the CMCS002 bench area.

- 2. Plug the external power-supply into a wall outlet. If outside the U.S., make sure you received the Asian/European model and have an appropriate plug adapter (supply input voltage is 230V AC, 50/60Hz in some areas overseas).

- 3. Connect the external power supply to P1 (0.65 mm DC jack). If a power supply was not ordered, then connect 3.3V to header pin P3-H1 and GND to header pin P3-H2.

- 4. Your CMCS002 evaluation module will power-up and start flashing the LED devices D1, D2, D3.

All pin headers are placed on 0.1 inch spacing to allow the use of standard prototyping "perf-board" with the CMCS002.

**WARNING!!** Do not directly connect 5V devices to the CMCS002 IO pins. See the section on 5V interfacing for proper connection methods.

# **2** Component Descriptions

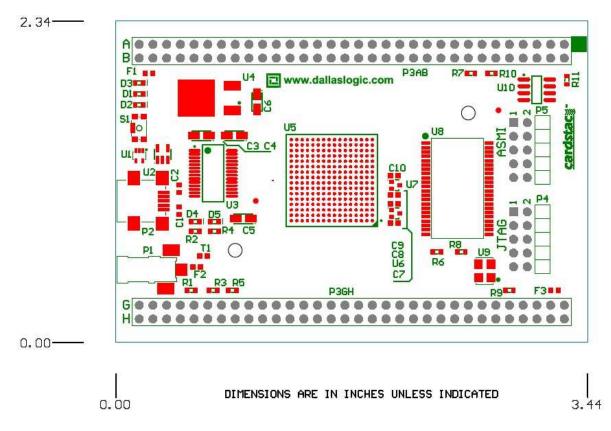

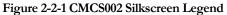

The following diagrams show a silkscreen image of the CMCS002 PCB, as well as a pin location diagram. You can use these images to help locate electronic devices and connector pin locations. Pin A1 is indicated by the green silkscreen square (white on the actual PCB).

Figure 2-2-2 PCB Pin Orientation

### 2.1 Altera Cyclone III Device Resources

The CMCS002 module can be ordered with an Altera EP3C25 FPGA in the 256 pin BGA package (U5). The module comes with the –C8 speed grade device. The 256 pin devices provides the following programmable logic resources:

| FPGA                                    | EP3C25 |

|-----------------------------------------|--------|

| Logic Elements (apprx. 50 gates per LE) | 24624  |

| M9K RAM Blocks (9216 bits per block)    | 66     |

| RAM (K bits)                            | 594    |

| PLLs                                    | 4      |

| 18bit x 18bit multipliers               | 66     |

Table 2-1 EP3C25 FPGA Resources

Consult Altera's <u>Cyclone III Device Handbook</u> for detailed information on internal device timing and design speed estimation. Some benchmark numbers for Altera's Nios II processor are also shown in the table below. These numbers are taken directly from Altera's "**Nios II Performance Benchmarks**" document (not from our own benchmarks). Note that the LE utilization for the Nios II does not include items such as a UART or timer. Both of these devices require approximately 75 LE each.

| Device    | Maximum             | Maximum             | LE          | LE          | LE          |

|-----------|---------------------|---------------------|-------------|-------------|-------------|

|           | Frequency /MIPS     | Frequency           | utilization | utilization | utilization |

|           | Nios Ile            | /MIPS Nios IIf      | Nios Ile    | Nios Ilf    | UART        |

| EP3C40-C6 | 215 MHz/ 30<br>MIPS | 175 MHz/194<br>MIPS | 650         | 1800        | 75          |

Table 2-2 Nios II Performance and Resource Utilization

### 2.2 CMCS002 Devices

#### 2.2.1 EPCS16 serial flash

The EPCS16 serial flash device (U10) is used to load the FPGA hardware configuration data. The EPCS16 device is a 16 Mbit device and contains 16,777,216 bits of program space. The EP3C25 FPGA requires 5.8 Mbits (non-compressed) for its configuration load, which leaves 10.2 Mbits for processor software images or user data. Cyclone III devices support compression of FPGA configuration loads. Compression will typically provide 35% - 50% reduction in space requirements of the configuration load. This can be implemented if more user data space is required. Note that the size of the compressed FPGA load is not fixed, and will vary from compile to compile. The EPCS16 device supports byte or buffer moves of data, and also has software driver and interface support via Altera's SOPC builder.

#### 2.2.2 512K X 8 SRAM

The 512K X 8 SRAM device (U8) is located on the top of the PCB. This device is primarily provided for Nios II or other CPU program and data storage. For Nios II processors (32 bit instruction), four SRAM access are required to fetch a single instruction. This is automatically handled by Nios dynamic bus sizing. The device is an IDT71V424S15PHG (or equivalent), which is an asynchronous SRAM with an access time of 15 ns. On the CMCS002 design, the SRAM has a dedicated address bus to the FPGA device, but the data bus (8 bit) is shared with external header pins. To disable the SRAM device, drive the SRAM CE pin high in your FPGA design.

#### 2.2.3 USB Interface

The CMCS002 board provides an FTDI FT232R device to support serial communications to your design. This device will allow terminal communications, or data transfer under program control. The FT232R supports low or high speed operating modes and data transfer rates up to 3Mbaud. A driver for the FT232R can be downloaded from the FTDI website. For more information on the FT232R, visit the manufacturer's web page at: http://www.ftdichip.com/Products/FT232R.htm

#### 2.2.4 JTAG and ASMI Programming Headers

Two separate 10 pin programming headers are provided on the CMCS002 module. One header is for the ASMI flash interface (P5) on the EPCS16/Cyclone III devices, and the other is for the Cyclone III JTAG port (P4). Two separate programming ports allows the CMCS002 design to support Flash reads and writes at the same time

the JTAG port is being used for operations like Altera SignalTap logic analyzer (Quartus II feature), or in-circuit debug. The ASMI port is used to program the FPGA flash image (.pof file) into the EPCS16 flash device. The JTAG port is used to program the SRAM image directly into the FPGA (.sof file). Note that pins 1 of both the JTAG (P4) and ASMI (P5) connectors are located towards the "top" of the PCB assembly (silkscreen "1" indicates pin 1 on each connector). When plugging in the Byte Blaster II or USB Blaster programmer, the red wire identifies pin 1 and the ribbon connector should be plugged in with the red wire towards the "top" (towards pin 1) on both P4 and P5. See section "CMCS002 FPGA Programming Instructions" for more details on ASMI and JTAG programming procedures.

#### 2.2.5 Reset Circuit

The CMCS002 module provides a TPS3802 voltage monitor (U2). The reset input of this device is active low and the device reset output drives the dedicated reset pin on the Cyclone III FPGA device. A Quartus II setting defines this Cyclone III FPGA pin to be either a dedicated chip wide reset or a user IO. Even if the pin is defined as user IO, the signal can still be used to reset individual circuits within a given design.

The TPS3802 will provide a 400mS reset pulse for the following events:

- Module power up

- Press of S1 push-button

- 3.3V power out of range

- Following FPGA configuration and loading

During FPGA initialization, the conf\_done (open drain) pin from the FPGA asserts the MR- (manual reset) input pin of the TPS3802 and causes a logic reset to the FPGA. Once the FPGA has finished loading, conf\_done will float high, and reset will de-assert approximately 400ms after FPGA configuration has finished. Note that this reset signal is driven locally to the FPGA only and is not connected to the PCB pin header (Cardstac reset). The FPGA must drive reset on the external pin via your design.

#### 2.2.6 FPGA User IO Bank Voltage

There are eight separate IO banks on the EP3C25 Cyclone III device. On the CMCS002 module, these eight banks are powered by 3.3V.

#### 2.2.7 Indicator LED

The CMCS002 module provides three general purpose LED outputs (green, yellow, red).

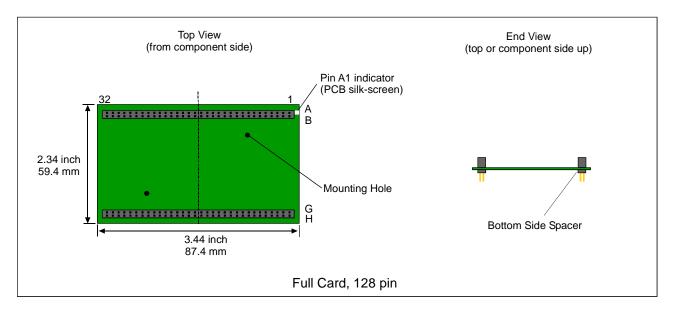

#### 2.2.8 CMCS002M IO Pin Information

The diagram below shows the CMCS002M module pin-out, and associated information (restrictions) on each 3C25 FPGA pin. This should be referred to (as well as the schematic) when designing with the CMCS002M. Note that a blank pin (no color) indicates an open FPGA IO pin. This table is also available in spreadsheet (.xls) format, and can be used to assign pin functions for your own project.

|            |               |      | _    |         | (B     | lank p   | in = | ope | en l | 10)                                              |

|------------|---------------|------|------|---------|--------|----------|------|-----|------|--------------------------------------------------|

|            | C             | ards | stad | 1       |        |          |      | -   | ar   | dstac                                            |

|            |               |      |      | -0.     | -      |          |      | 1   |      |                                                  |

|            |               | Н    | G    |         |        |          |      | В   | А    |                                                  |

|            | GND           | 32   | 32   |         | -      |          | vaux |     | 33   | 3.3V                                             |

|            | 1.8K pullup   | 31   | 31   |         | -      |          | 3.3V | 24  | 24   | GND                                              |

|            | 1.8K pullup   | 30   | 30   |         |        |          | 3.3V | 30  |      | dedicated rst io pin with 1.8K pullup, tied to h |

|            | 1.ok pullup   | 29   | 29   |         |        |          | -    | 29  | 29   |                                                  |

|            | 1.8K pullup   | 28   | 28   |         |        |          |      | 28  | 28   |                                                  |

|            | noreputup     | 27   | 27   |         |        |          |      | 27  | 27   |                                                  |

|            | GND           | 26   | 26   |         |        |          |      | 26  |      | input only (fpga clkpin)                         |

|            |               | 25   | 25   |         | 1      |          |      | 25  |      | GND                                              |

|            |               | 24   | 24   |         |        |          |      | 24  | 24   |                                                  |

|            |               | 23   | 23   |         |        |          |      | 23  | 23   |                                                  |

|            |               | 22   | 22   |         |        |          |      | 22  | 22   |                                                  |

|            |               | 21   | 21   |         | 2 - Pi |          |      | 21  | 21   |                                                  |

|            | GND           | 20   | 20   |         |        |          |      | 20  | 20   |                                                  |

|            |               | 19   | 19   |         |        |          |      | 19  | 19   | GND                                              |

|            |               | 18   | 18   |         |        |          |      | 18  | 18   |                                                  |

|            |               | 17   | 17   |         | -      |          | -    | 17  | 17   |                                                  |

|            |               | 16   | 16   |         | Î.     |          |      | 16  | 16   |                                                  |

|            |               | 15   |      | CMCS002 | SRAM   | data bus | -    | 15  | 15   |                                                  |

|            | GND           | 14   |      | CMCS002 |        |          |      | 14  |      | input only (fpga clkpin)                         |

|            |               | 13   |      | CMCS002 |        |          | -    | 13  | 13   | GND                                              |

|            |               | 12   |      | CMCS002 |        |          | -    | 12  | 12   |                                                  |

|            |               | 11   |      | CMCS002 |        |          |      | 11  | 11   |                                                  |

|            |               | 10   |      | CMCS002 |        |          | -    | 10  | 10   |                                                  |

|            | 1             | 9    | 9    | CMCS002 | SRAM   | data bus |      | 9   | 9    |                                                  |

|            | GND           | 8    |      | CMCS002 |        |          |      | 8   | 8    | input only (fpga clkpin)                         |

| input only | (fpga clkpin) | 7    | 7    |         |        |          |      | 7   |      | GND                                              |

|            |               | 6    | 6    |         |        |          |      | 6   | 6    | input only (fpga clkpin)                         |

|            |               | 5    | 5    |         |        |          |      | 5   |      | 1.8K pullup                                      |

|            |               | 4    | 4    |         |        |          |      | 4   | 4    |                                                  |

|            | tied to A30   | 1    | 3    | -       |        |          |      | 3   |      | 1.8K pullup                                      |

|            | GND           | 2    | 2    |         |        |          |      | 2   | 2    | 1.8K pullup                                      |

|            |               | 1    |      | vaux    |        |          |      | 1   | 1    | GND                                              |

# **3 Setup and Programming**

## 3.1 CMCS002 Module Setup

Steps to setup and run your CMCS002 module are:

- 1. Locate the PCB and module so as to not short any of the pins on the bottom of the PCB. Make sure to clean away any loose wire or solder from the CMCS002 bench area.

- 2. Connect the ByteBlaster II or USB Blaster cable to P4 (JTAG) programming header.

- 3. Plug the external power-supply into a wall outlet. If outside the U.S., make sure you received the Asian/European model and have an appropriate plug adapter (supply input voltage is 230V AC, 50/60Hz in some areas overseas).

- 4. Connect the external 3.3V power supply to P1 (0.65mm DC jack). If a power supply was not ordered, then connect 3.3V to header pin P3-H1 and GND to header pin P3-H2.

The CMCS002 module will run and start to flash the LED devices.

Note that the CMCS002 module can accept 3.3V input voltage via the 0.65mm DC jack (P1-center pin positive). It can also be powered by using pin H1 (3.3V) and pin H2 (GND) of P3. Pin H2 is a ground pin, and pin H1 is a 3.3V power pin. P3-H1 can be used to input power to the CMCS002, or if the DC JACK is attached to the CMCS002, then pin H1 can provide power to external circuits. Do not connect the DC JACK to the CMCS002 if you have 3.3V attached to pin H1 from another power source. Note that pins H1, G2, B31, and A32 are all 3.3V power pins. The current limit for each pin is 2 Amps. The CMCS002 is designed to <u>operate at **3.14** – **3.46V** (3.3V +/- 5%) and requires approximately 500 mA of current with a minimal FPGA design. Do not exceed this voltage specification when applying external power.</u>

#### 3.1.1 Altera Software and FPGA Programmer

Your CMCS002 requires Altera's Quartus II development software, and an FPGA programming device (included in the kit). Quartus II should be installed on your PC to provide FPGA design and Nios II/SOPC support (Nios II/SOPC install is optionall). Quartus II is used to compile your design files and Program the Cyclone III FPGA on the CMCS002 module (via the FPGA programmer cable). Nios II/SOPC installation is required only to support implementation of Nios II processor designs. Quartus II version 9.0 for Windows requires Microsoft Windows Vista or XP. If using the web edition, you will be required to request a web edition license from Altera, even though the software is free of charge. Linux versions of Quartus II 9.0 require a full (paid) license.

Web edition Quartus II provides incredible design capability and fully supports the Cyclone III line of FPGA devices (web edition has limited compile functionality for Stratix and higher end FPGA devices). The web edition of Nios II/SOPC builder is a trial version and implements a "tether" limitation for Nios II processors. This means that a Nios II processor instantiated with trial software will quit functioning if disconnected from the Altera programmer. For learning or testing on the CMCS002 module this is not a serious limitation, but to implement working Nios II designs for your own products, you will have to acquire a full Nios license.

The ByteBlaster II cable is connected to the LPT (printer) port of your Windows/Linux PC. The USB Blaster is connected to a USB port. For detailed information on Quartus II/Blaster installation, setup, and requirements access <u>www.altera.com</u> and reference their online documentation.

#### 3.1.2 CMCS002 FPGA Programming Instructions

The CMCS002 FPGA device can be programmed at any time using the JTAG port (using a .sof file), or by the EPCS16 serial flash device at board power up. A non-volatile flash image is loaded into the EPCS16 device (using a .pof file) by the user via the ASMI port. The two possible methods for programming the CMCS002 Cyclone III FPGA device are:

- Use a .sof file and program the FPGA directly. To do this, connect the Byte-blaster to the JTAG port. Open the Altera programmer software and be sure "JTAG" Mode is selected. Next, click the "Auto Detect" button. Right click on the FPGA device that is listed and select "Change file". This will allow you to select a .sof file and assign it to the listed device. Finally, click the "Start" button to program the FPGA device. This is a temporary load. If power is removed the FPGA must be re-programmed.

- 2. Use a .pof file and permanently flash a new load into the EPCS16 device via the ASMI interface. To do this, attach the Byte-blaster to the ASMI port. Open the Altera programmer software and change to "Active Serial Programming" Mode. Select "Add file" and browse to your project .pof file. Finally, make the desired programming selections (check mark) and press the "Start" button. This will store the FPGA load in the serial flash device. Cycle power on the CMCS002 board to load the flash image into the FPGA device. Note that you cannot "auto-detect" on the ASMI port. Important: when the project file was compiled, you must have selected the EPCS16 as the target device and the mode as "Active Serial Programming". Other selections such as "Generate compressed bit-streams" must also be assigned at this time. These selections are found under the "Assignments Device" menus in Quartus II (click the "Device and Pin Options" button and select the "Configuration" tab).

#### 3.1.3 Cyclone III Pin Voltage Sensitivity (over-shoot and under-shoot)

Cyclone III FPGA device IO pins are sensitive to over-voltage and under-voltage conditions (under 0V and over 3.3V). This includes over-shoot and under-shoot from un-terminated signal lines. Make sure to include series termination where possible, and check over-shoot and under-shoot on all IO pins. Also, if driving signals to the Cyclone III FPGA from another FPGA device, reduce the amount of drive current that is programmed in the driving FPGA design to a minimum. Refer to Altera application note AN-447-1.1, **Interfacing Cyclone III Devices with 3.3/3.0/2.5-V LVTTL/LVCMOS I/O Systems** for more information. Cyclone III devices implement PCI clamping diodes on pins which are **not** configured for device programming to protect against over-voltage conditions. For example, active serial configuration pins ASDO and nCSO do not provide clamping diodes when used for programming operations. Clamping diodes are connected between the signal pin, and the VCCIO rail of the board (3.3V on the CMCS002). Usually, series resistors can be implemented to protect device inputs (clamping diodes) from over-current damage. The Cyclone III clamping diodes have a sink current limit of 10 mA DC.

#### 3.1.4 5V Interfacing With Cyclone III

**WARNING!!** Do not directly connect 5V devices to the CMCS002 IO pins. Read further for proper 5V connection methods.

Cyclone III devices do not directly support 5V VIO and therefore 5V interfacing techniques must be implemented. All Cyclone III devices use PCI clamping diodes on pins which are not configured for device programming (for example, active serial configuration pins, ASDO, nCSO). Normally, series resistors can be implemented to protect device inputs (clamping diodes) from over-current damage. Cyclone III devices, however, are very sensitive to over-voltage and under-voltage, even from conditions like signal ringing on un-

terminated lines. Because of the sensitive nature of Cyclone III devices, a 5V translator IC should be utilized when interfacing to 5V devices.

Make sure you **properly translate any 5V circuits** that are connected to the CMCS002 module to 3.3V levels using an appropriate translator IC. Improper connection of 5V circuits can **damage the CMCS002 Cyclone III FPGA** or the external components that you are interfacing to.

#### 3.1.5 CMCS002 Module Power

The CMCS002 3.3V power plane is sourced from pin groups H1/G2 and B31/A32. Each pin on the CMCS002 is rated at 2 Amps. Each pin group (H1/G2 and B31/A32) is fused at 3 Amp. The CMCS002 3.3V power rail should operate in the range of 3.14V - 3.46V. Pin group H1/G2 is protected with fuse F3, pin group B31/A32 is protected with fuse F1, and the 3.3V DC jack input P1 is protected by fuse F2. The CMCS002 kit power supply (via P1 DC jack) can be used to supply 3.3V power to circuits external to the CMCS002 module (via pin header pins). If the opposite scenario is implemented, and power is to be supplied to the CMCS002 module via the header pins (3.3V), do not plug the external power supply into the DC jack (power applied by both header pins and the DC jack). Make sure you do not exceed the fuse limitation of the CMCS002 module when connecting and powering external devices.

| 3.3V Input        | Current Limit | Fuse |

|-------------------|---------------|------|

| DC Jack (P1)      | 2.5 A         | F2   |

| Pin Group H1/G2   | 3A            | F3   |

| Pin Group B31/A32 | 3A            | F1   |

Table 3-1 CMCS002 Power Input Fusing

Even though two separate pin groups are implemented which uses two fuses, both of these pin groups are connected to the same 3.3V rail on the CMCS002 (to support installation of two separate Cardstac half cards). This implies that the effective current limit on all four pins (H1, G2, B31, A32) is 6 Amps. These four pins MUST be connected to the same external 3.3V supply.

#### 3.1.6 Cardstac Support – CMCS002 Design

The CMCS002 was designed to support the Cardstac specification. The following header pins on P3 have 1.8K Ohm pull-up resistors attached:

Pin H3 (RST-), R9 Pin A2 (1I2C\_SCL), R11 Pin A3 (1I2C\_SDA), R10 Pin A5 (IRQ4B-), R7 Pin H28 (IRQ0A-), R5

Pin H30 (0I2C\_SDA), R3

Pin H31 (0I2C\_SCL), R1

These resistors can be removed if pull-ups are not required. For more information on Cardstac, download the specification located at <u>www.dallaslogic.com</u>.

#### 3.1.7 Altera Reference Documents

This User Manual is a guide to the CMCS002 reference design as well as a guide for basic Quartus II programming operations. It is not intended to replace the standard set of Altera documentation that is necessary for detailed design of Cyclone III FPGA systems. All of Altera's documentation is available online at www.altera.com.

## 4 CMCS002 Design Information

### 4.1 Pin Function Mapping

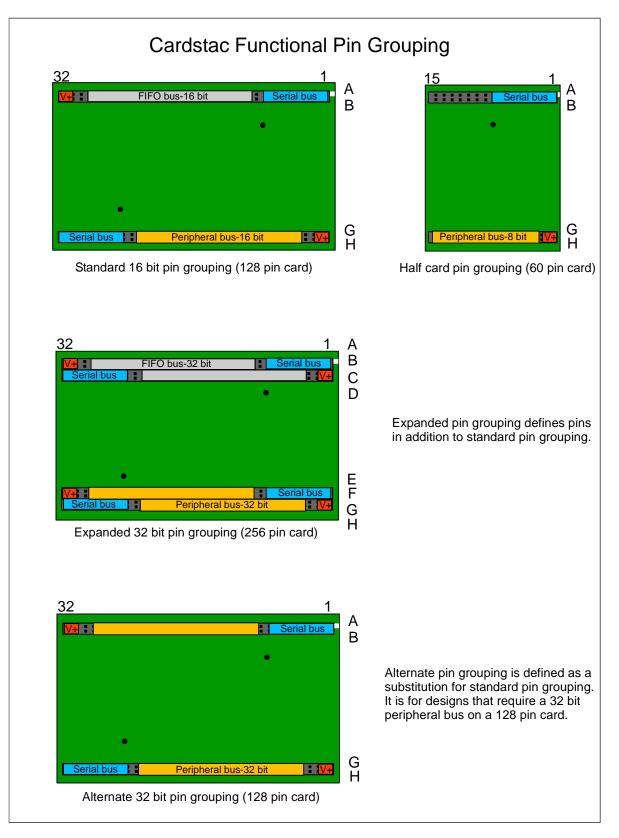

For additional information on CMCS002 pin function mapping, refer to the Cardstac specification available for download from <u>www.dallaslogic.com</u>. Because the CMCS002 is an FPGA based module, all signal pins can be programmed as IO (both input and output). The Quartus II starter design defines FPGA pin locations. The CMCS002 module is a Cardstac standard card (128 pins on two stack-through pin headers). The stack-through pin headers provide four 3.3V power in pins, twelve GND pins, and 110 signal pins. There are also 2 pin locations that are reserved for 12V power input (not implemented on CMCS002). The following two diagrams show recommended pin function mapping for the CMCS002M module. Note that the gray highlighted pins indicate synchronous FIFO bus functions. Yellow highlighted pins clock, reset, and power functions.

| PIN | ROW A         | ROW B           | ROW G           | ROW H            |

|-----|---------------|-----------------|-----------------|------------------|

| 1   | GND           | 1SPI_CLK        | VAUX0 / +12V    | +3.3V            |

| 2   | 1I2C_SCL      | 1SPI_MOSI/5TX   | +3.3V           | GND              |

| 3   | 1I2C_SDA      | 1SPI_MISO/5RX   | CS0-            | RST-             |

| 4   | IRQ5B- / 4CTS | 1SPI_SSN3-/4TX  | CS1-            | ADD0             |

| 5   | IRQ4B- / 3CTS | 1SPI_SSN2-/3TX  | CS2-            | ADD1             |

| 6   | S-CLK4        | 1SPI_SSN1-/4RTS | CS3-            | ADD2             |

| 7   | GND           | 1SPI_SSN0-/3RTS | CS4-            | CLK0             |

| 8   | S-CLK3        | IRQ7B- / 4RX    | DATA0           | <mark>GND</mark> |

| 9   | S-DP1         | IRQ6B- / 3RX    | DATA1           | WRITE-           |

| 10  | S-DP0         | S-D15 / IO7B    | DATA2           | ADD3             |

| 11  | S-STAT9       | S-D14 / IO6B    | DATA3           | ADD4             |

| 12  | S-SYNC-       | S-D13 / IO5B    | DATA4           | ADD5             |

| 13  | GND           | S-D12 / IO4B    | DATA5           | READ-            |

| 14  | S-CLK2        | S-D11 / IO3B    | DATA6           | GND              |

| 15  | S-STAT8       | S-D10 / IO2B    | DATA7           | ADD6             |

| 16  | S-STAT7       | S-D9 / IO1B     | DATA8 / IO0A    | ADD7             |

| 17  | S-STAT6       | S-D8 / 100B     | DATA9 / IO1A    | ADD8             |

| 18  | S-CLK1        | S-D7            | DATA10 / IO2A   | ADD9             |

| 19  | GND           | S-D6            | DATA11 / IO3A   | ADD10            |

| 20  | S-READ-       | S-D5            | DATA12 / IO4A   | GND              |

| 21  | S-STAT5       | S-D4            | DATA13 / IO5A   | ADD11            |

| 22  | S-STAT4       | S-D3            | DATA14 / IO6A   | ADD12            |

| 23  | S-STAT3       | S-D2            | DATA15 / IO7A   | ADD13            |

| 24  | S-WRITE-      | S-D1            | IRQ2A- / 0RX    | ADD14 /WAIT-     |

| 25  | GND           | S-D0            | IRQ3A- / 1RX    | ADD15 /BE0-      |

| 26  | CLK1 (S-CLK0) | S-SEL4          | 0SPI_SSN0-/0RTS | GND              |

| 27  | S-STAT2       | S-SEL3          | 0SPI_SSN1-/1RTS | ADD16 /BE1-      |

| 28  | S-STAT1       | S-SEL2          | 0SPI_SSN2-/0TX  | IRQ0A- /0CTS     |

| 29  | S-STAT0       | S-SEL1          | 0SPI_SSN3-/1TX  | IRQ1A-/1CTS      |

| 30  | RST-          | S-SEL0          | 0SPI_MISO/2RX   | 0I2C_SDA         |

| 31  | GND           | +3.3V           | 0SPI_MOSI/2TX   | 0I2C_SCL         |

| 32  | +3.3V         | VAUX0 / +12V    | 0SPI_CLK        | GND              |

### Table 4-1 Recommended Pin Mapping (16 bit interface)

Figure 4-4-1 Recommended Functional Pin Grouping

### 4.2 Quartus II Starter Design

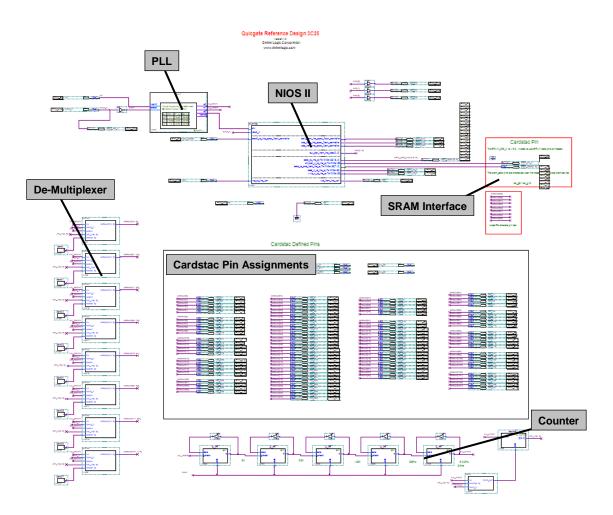

The starter design was created to provide a board level functional test for the CMCS002. The design includes a Nios II soft controller, PLL, de-multiplexer circuit, counter circuit, SRAM interface and Cardstac pin definitions. The design exercises the onboard SRAM, LEDS and UART by executing a program from onboard memory. The Cardstac I/O pins are driven using the counter and de-mux circuits, these circuits place a pulse train on the user pins allowing users to view the output using an oscilloscope. The PLL uses the onboard 25Mhz. clock to create a 20MHz. clock for the NIOS II controller and a 10KHz clock for the counter circuit. The Cardstac I/O are driven from a 312Hz. counter that is derived from the 10Khz. clock signal. The figure below identifies the functional blocks located in the starter design.

Figure 4-4-2 Starter Design Block View

The figure below shows the NIOS II block symbol for the CMCS002 starter design. The Nios II design is comprised of an SRAM interface, UART interface, LED interface and EPCS controller interface. The SRAM interface was designed using SOPC builder's custom component wizard. All remaining interfaces were created using predefined SOPC builder components. The SRAM interface component is included with the starter design reference files.

| clk<br>reset_n                     |                                                                                                                                                                      |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| data0_to_the_epcs_flash_controller | dclk_from_the_epcs_flash_controller<br>sce_from_the_epcs_flash_controller<br>sdo_from_the_epcs_flash_controller                                                      |

|                                    | out_port_from_the_leds[20]                                                                                                                                           |

|                                    | addr_to_the_cy7c1049cv33[180]<br>chipsel_n_to_the_cy7c1049cv33<br>data_to_and_from_the_cy7c1049cv33[70]<br>read_n_to_the_cy7c1049cv33<br>write_n_to_the_cy7c1049cv33 |

| rxd to the uart                    | txd from the uart                                                                                                                                                    |

NOTE: The starter design was created using Quartus II ver. 9.0 SP1. Some user modification of the starter design may be required to support compilation under later versions of Quartus II. Quartus II "web edition" is available for download from the Altera website. This starter design is provided "as is". Modification or support of the Nios II starter design is not included in the purchase price of the CMCS002 module.

Your CMCS002 module comes with the CMCS002 starter design stored in the EPCS16 flash device. After applying power to the module, the LED devices will illuminate, and the module IO pins will be toggled by a CMCS002 counter circuit. All of the FPGA IO pins are defined making it an easy job to connect nets of your own logic circuits to external pins. To modify and add to the design, you will need to obtain the starter design Quartus II project archive (.qar file). This file is available upon request from us at requests@dallaslogic.com. This file should be "de-archived" to a project folder located on your PC.

For the CMCS002 starter design, Altera "mega-function" blocks were instantiated for logic circuit functionality, and then graphical representations of those blocks (.bdf files) were "stitched" together using Altera's graphic schematic editor. This creates the top-level graphical ".bdf" design file (hierarchical design) from which, it is very easy to analyze and interpret design intent. Quartus II supports VHDL, and Verilog HDLs The graphical representations of these HDL blocks can also be added to the top-level design file.

#### 4.2.1 CMCS002 Starter Design File Install

Please read the README file provided with the starter design for detailed installation directions.

#### 4.2.2 Quartus II Tutorial Instructions

After installation of your Quartus II web edition CD, it is highly recommended that you go through the exercises contained in the Quartus II tutorial. The tutorial will help you to become comfortable with the QII 9.0 development environment.

Launching QII:

- Double click the Quartus II shortcut (icon) found on the desktop of your computer (or navigate to the Altera folder and double click the Quartus II program icon).

- Allow the computer to search the Altera site for updates. This will ensure that you have the latest copy of web edition.

- Under the Help menu on the top toolbar, select tutorial.

- At the top of the tutorial window push the Next button this will take you through tutorial basics and into the design sections.

Once you have completed the tutorial sections you will be ready to explore the CMCS002 design.

The CMCS002 design project can be opened from the "CMCS002.qpf" file located in the CMCS002 project directory. The CMCS002 design top level module (top.bdf) was created using Altera's schematic editor. The schematic allows the user to create graphical block representations for sub-modules. These sub-modules can then be stitched together using "wires" for connectivity.

#### 4.2.3 CMCS002 Design Schematic

CMCS002 schematic pages should be referenced for details on circuit design or when connecting devices to the supplied pin-headers. The schematic (.pdf file) pages are available upon request. Please send us an email at requests@dallaslogic.com to receive a copy of the schematic.

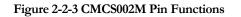

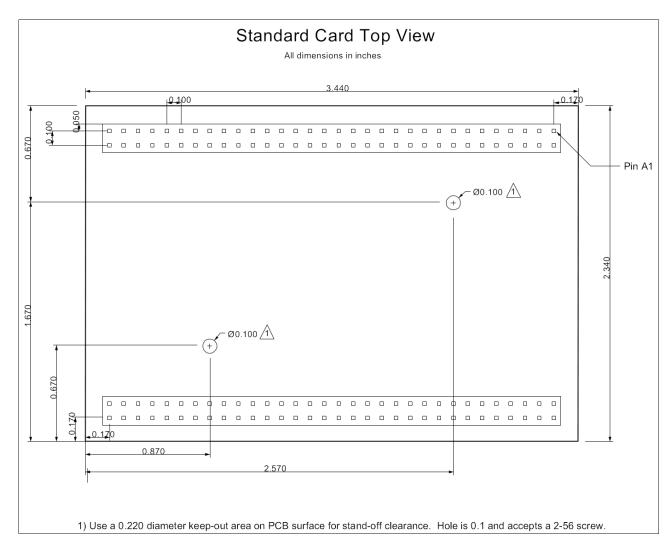

# **5** Mechanical Dimensions

The mechanical dimensions for the CMCS002 module are shown in the diagram below.

Figure 5-5-1 CMCS002 Mechanical Dimensions

# 6 Ordering and Technical Help

#### 6.1.1 CMCS002 Ordering Information

CMCS002 and related products can be ordered directly from our website at <u>www.dallaslogic.com</u>. Orders can be shipped to almost any destination in the world. Shipping costs for orders to be delivered outside the continental U.S. can be obtained on the website before the order is finalized (submitted). CMCS002 part numbers which are available for ordering are shown in the table below:

| Part Number     | Altera FPGA/Loader Device  | Description             |

|-----------------|----------------------------|-------------------------|

| CMCS002-2M-8    | EP3C25F256C8N / EPCS16SI8N | EP3C25 module           |

| CMCS002-2M-8-KB | EP3C25F256C8N / EPCS16SI8N | EP3C25 Byte Blaster kit |

| CMCS002-2M-8-KU | EP3C25F256C8N / EPCS16SI8N | EP3C25 USB Blaster kit  |

#### 6.1.2 CMCS002 Module Technical Help

Being an "internet-centric" company, Dallas Logic provides manned 24hr email and web forum support. The best way to obtain help with problems is to post questions to our online support forum. We are prompt about replying, and there is also a good chance you will find your question has already been answered online in the forum. If you prefer email support, we can be reached at <a href="mailto:support@dallaslogic.com">support@dallaslogic.com</a>. We will generally reply within 24hrs of receiving an inquiry or request for help with problems that are related to the operation of your CMCS002 module. Before contacting us with inquiries, please make sure you have:

- 1. Verified fuses F1, F2, and F3 (located on the top side of the PCB) and checked the 3.3V input level at header pin P3-H1.

- 2. Removed any test circuits from connection to the CMCS002 PCB and restored it to its original design state (remove any modifications and restore original circuits).

- 3. Re-programmed and tested your CMCS002 module with the original reference design file.

For questions related specifically to Altera software tools or FPGA devices, we can sometimes be of assistance, but will generally refer you to the Altera online knowledge base or online support web pages.

#### 6.1.3 Warranty Information

Your un-modified CMCS002 assembly is guaranteed to be free of defects in material and workmanship for a period of ninety days from the date of purchase. If your CMCS002 module stops working during the ninety day period, and is in its original, un-modified state, first contact us at <a href="mailto:support@dallaslogic.com">support@dallaslogic.com</a>. If the problem cannot be resolved, you must return the PCB assembly and power supply, postage prepaid to Dallas Logic Corporation. All repairs and return ship will be made within 10 days of receipt of package. During the warranty period, Dallas Logic will, at its option, repair, replace, or refund the purchase price. Products that have been damaged or modified from their original design state are not covered by warranty. No warranty is implied with respect to the software or firmware files.

## 7 Disclaimer

Information in this document concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. Customers are advised to obtain the latest version of device specifications before relying on any published information. Dallas Logic Corporation DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DATA FILES, DEVICES, OR TECHNOLOGY described in this document. Dallas Logic Corp. also does not assume liability for intellectual property infringement related in any manner to use of information, devices, or technology described herein or otherwise. Dallas Logic Corp. makes no warranty of merchantability or fitness for any purpose and does not assume liability for damages incurred to property due to the use of this product or implementation of information or procedures listed in this document. Use of information or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.